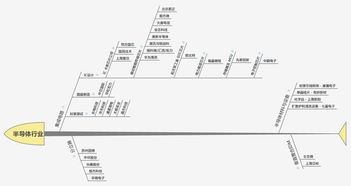

集成電路設計 從概念到實體的技術藍圖

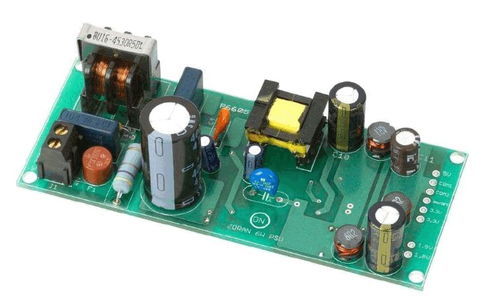

集成電路設計是現代電子工業的核心環節,它涉及將復雜的電子系統功能轉化為可在微小硅片上實現的物理結構。設計過程通常包括多個層次,從系統級設計到物理實現,每一步都至關重要。

在系統級設計階段,工程師定義芯片的整體功能和性能指標,例如處理速度、功耗和面積。這一階段通常使用高級建模語言(如SystemVerilog或VHDL)進行行為描述,確保設計滿足應用需求。

接下來是邏輯設計,工程師將系統功能轉化為邏輯門和寄存器傳輸級(RTL)代碼。這一步驟通過仿真驗證邏輯正確性,并優化電路結構以減少延遲和功耗。常用的工具有Synopsys Design Compiler和Cadence Genus,它們幫助自動化邏輯綜合過程。

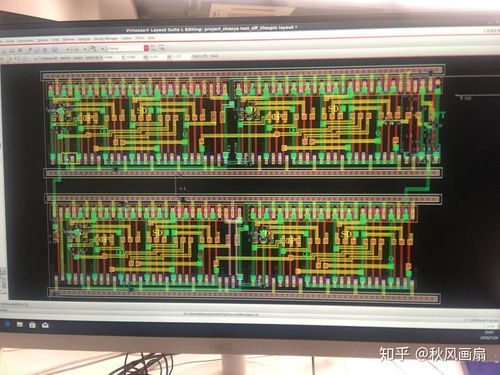

物理設計是集成電路設計的關鍵視圖之一,涉及將邏輯電路映射到實際的硅片布局。這包括布局規劃、電源網絡設計、時鐘樹綜合和布線。工具如Cadence Innovus和Synopsys IC Compiler支持這一過程,確保電路在制造后能穩定運行。物理設計還必須考慮制造約束,例如光刻限制和熱管理,以避免缺陷。

驗證貫穿整個設計流程,包括功能驗證、時序驗證和物理驗證。通過仿真、形式驗證和原型測試,工程師確保芯片在真實環境中無誤工作。隨著工藝節點不斷縮小(如7納米或5納米),設計復雜度增加,驗證變得尤為重要。

集成電路設計視圖不僅關注技術實現,還涉及多學科協作。設計師需要與工藝工程師、軟件開發者緊密合作,以平衡性能、成本和上市時間。隨著人工智能和物聯網的興起,集成電路設計將更注重能效和集成度,推動創新應用發展。集成電路設計是電子技術進步的基礎,它通過精密的視圖規劃,將創意轉化為改變世界的芯片產品。

如若轉載,請注明出處:http://www.archlink.com.cn/product/24.html

更新時間:2026-01-07 02:22:40