集成電路設計 創新驅動未來科技發展的核心引擎

集成電路設計作為現代信息技術和電子工業的基石,不僅推動了電子產品向小型化、智能化和高效能方向發展,更是在全球科技競爭中占據重要地位。隨著人工智能、5G通信和物聯網技術迅猛發展,集成電路設計行業迎來了前所未有的機遇與挑戰。本文將從設計流程、關鍵技術、行業趨勢和人才培養四個方面,深入探討這一領域的現狀與未來。

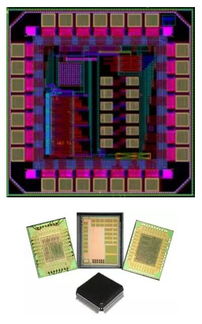

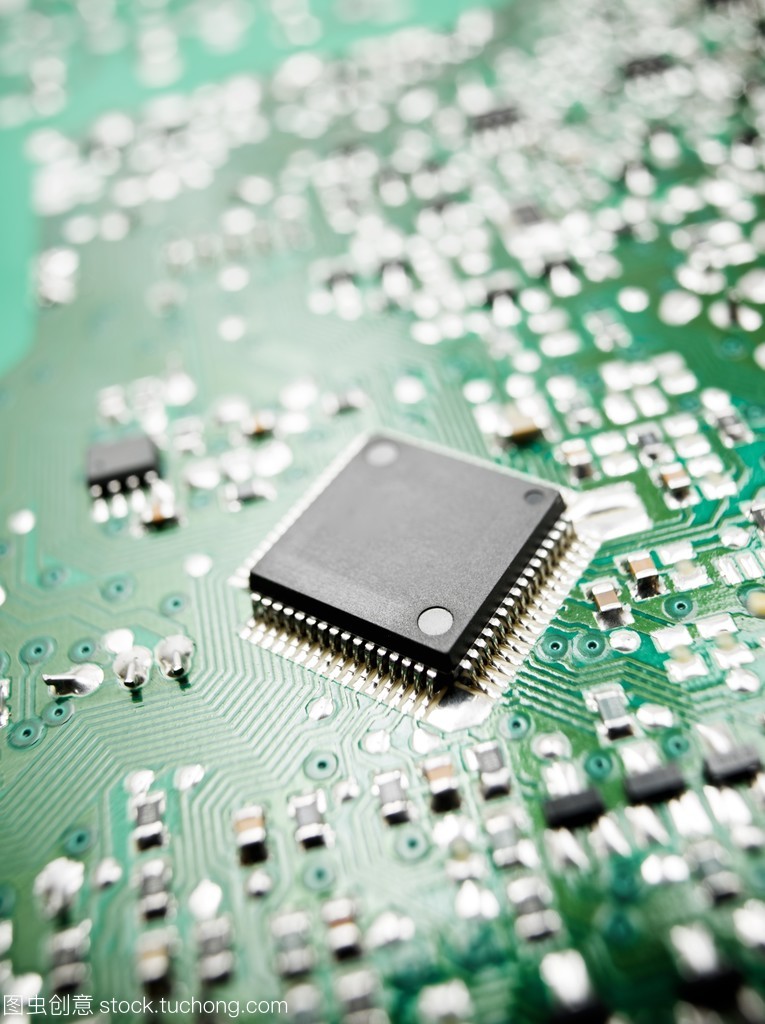

集成電路設計流程通常包括系統規格定義、架構設計、邏輯設計、物理設計和驗證測試等環節。設計師需要根據應用需求,確定芯片的功能、性能和功耗指標,隨后利用硬件描述語言(如Verilog或VHDL)進行邏輯建模,再通過電子設計自動化(EDA)工具完成布局布線。物理設計階段涉及晶體管級優化和信號完整性分析,最終通過流片和測試實現芯片量產。整個流程要求設計團隊具備跨學科知識,包括半導體物理、計算機架構和算法優化。

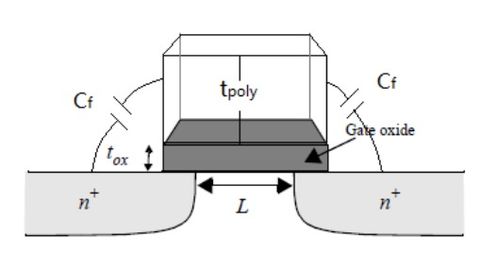

在關鍵技術方面,先進制程工藝、異構集成和低功耗設計成為焦點。7納米及以下工藝節點使得單位面積晶體管數量倍增,但同時也帶來量子隧穿效應和熱管理難題。三維集成電路(3D-IC)技術通過垂直堆疊芯片,突破了傳統平面集成的性能瓶頸。隨著邊緣計算和可穿戴設備普及,近閾值電壓設計和動態電源管理技術大幅提升了能效比。這些創新不僅依賴于EDA工具的迭代升級,更需要算法與硬件的協同優化。

當前行業呈現出多元化與生態化發展趨勢。一方面,云計算巨頭紛紛定制專用集成電路(ASIC)以優化數據中心能效,例如谷歌的TPU和亞馬遜的Inferentia;另一方面,開源指令集架構(如RISC-V)降低了設計門檻,催生了面向物聯網的輕量級芯片創業潮。與此全球供應鏈重組和地緣政治因素促使各國加強本土芯片制造能力,中國在《集成電路產業促進政策》支持下,正加速構建從設計到封測的完整產業鏈。

人才培養是支撐行業可持續發展的關鍵。高校需強化微電子專業與人工智能、材料科學的交叉課程,企業則應通過產學研合作共建實訓平臺。值得注意的是,軟硬件協同設計能力已成為招聘市場的新要求,工程師既要掌握傳統電路設計方法,也需熟悉機器學習在芯片優化中的應用。國際半導體產業協會(SEMI)數據顯示,到2025年全球集成電路設計人才缺口將達30萬人,這要求教育體系與產業需求實現更緊密對接。

量子芯片、存算一體架構和生物啟發的神經形態計算將重塑集成電路的設計范式。隨著碳納米管、二維材料等新型半導體走向實用化,下一代芯片有望突破硅基物理極限。在這個過程中,設計方法論需從“性能優先”轉向“能效-安全-可靠性”多維平衡,以支撐智慧城市、自動駕駛等關鍵場景的應用需求。唯有通過持續的技術創新與產業協同,集成電路設計才能繼續擔當數字化時代的引擎,為人類社會發展注入不竭動力。

如若轉載,請注明出處:http://www.archlink.com.cn/product/7.html

更新時間:2026-01-07 08:28:55